# **ZYBO Video Workshop**

Paris, FRANCE

23.03.2017

# 1 Theoretical background

Software is everywhere. The flexibility it offers to designers allows it to be used in a multitude of applications. Many consumer, industrial or military products are either running software or began as a software model or prototype executing on a generic circuit, or processor. Decades of advances in software engineering resulted in ever higher abstractions, ever smarter tools, ever increasing number of automatic optimizations that improve code re-use, shorten design time and increase performance. Continuous performance increase quantified by the number of instructions executed per second has been driven at first by the increase in processing frequencies, then by parallelization of algorithms and simultaneous execution of tasks by multiple processing cores.

The ubiquitous nature of software lead to most of the engineering problems to be approached with software solutions at first. Depending on the application a software-only approach might not meet the requirements, be those latency, throughput, power or other. An expensive option would be handing the algorithm over to a hardware engineer for a custom circuit implementation. The entry cost of application-specific integrated circuit (ASIC) design is still high despite advancements in fabrication technologies. Depending on the product forecasts, and ASIC design might not be viable economically.

Bridging the gap between generic processor circuits and ASICs are FPGAs, allowing the use of blank reprogrammable hardware logic elements to implements a custom circuit. It offers a lower barrier of entry to power savings and performance benefits of fabrication technologies without the cost of ASIC. Also, an algorithm optimized for FPGA implementation benefits from the inherently parallel nature of custom circuits.

#### 2 Hardware

The Digilent Zybo development board is well-suited for prototyping an algorithm running in software at first and then off-loading sub-tasks for processing to custom circuits. It is based on a Xilinx Zynq 7010 SoC, a hybrid between a dual-core ARM A9 (processing system, PS) and Artix-7 based FPGA (programmable logic, PL). Low-latency, high-throughput coupling between PS and PL allows for software implementation, where design-time is more important than performance, and hardware, where performance is critical.

The programming model for software usually makes use of programming languages that abstract from hardware particularities. While this offers increased portability and ways to apply automatic compiler optimizations, avoiding knowledge about the underlying hardware is not possible anymore close to the performance limits.

FPGA design can make use of two different programming models. One is RTL description in VHDL/Verilog, the other is high level synthesis in C/C++. High level synthesis represents a somewhat similar programming model to software programming. However, for a worthwhile improvement over software implementation of the same algorithm, one needs to have a good understanding of the underlying hardware architecture. Much more so than for software in general.

#### 2.1 FPGA Architecture

Field programmable gate array (FPGA) is a large array of configurable logic blocks (CLB), interconnect wires and input/output (I/O) pads. The CLB is made up of look-up tables (LUT) and flip-flops (FF), in

varying numbers depending on the exact FPGA architecture. This structure is generic enough to implement any algorithm. During programming the LUTs are programmed to implement a certain logic function, and FFs to pipeline the data flow synchronous to a clock signal. Interconnect is also programmed to wire LUTs, FFs, input pads and output pads together resulting in a custom hardware circuit implementing a certain algorithm.

Current FPGA architecture also include hard primitive blocks that specialize a certain function that would otherwise be too costly in terms of logic utilization or too slow in terms of throughput to implement in generic logic. For example, digital signal processing (DSP) blocks are available to implement a multiply-accumulate circuit with no generic logic utilization. These blocks are optimized enough to offer superior performance for the specific task. Another example is dual-port static RAM (BRAM), that offers higher capacities than RAM implemented in LUTs. These primitive blocks are by default automatically inferred for certain HDL constructs like the multiply operator (\*) for DSP or array access for BlockRAM.

LUT is a memory element that implements a truth-table. Depending on the exact architecture, each LUT has a number of inputs that address a location in the truth-table. The value stored at that address is the output of the function implemented. During programming the truth-table is populated to implement the desired function. It can also be thought of and used as a 2<sup>N</sup>-memories, called distributed RAM. It is a fast memory type because it can be instantiated all over the FPGA fabric, local to the circuit that needs data from it.

FF is a storage element that latches new data on its input when clock and clock enable conditions are true and permanently provides the stored data on its output.

BRAM is a dual-port RAM that stores a larger set of data. It holds 18Kb or 36Kb and can be addressed independently over two ports for both read and write. In essence, two memory locations can be accessed simultaneously in the same clock cycle.

#### 2.2 Parallelism and program execution

A processor core executes software instructions in a sequence. Higher-level programming languages translate language statements into assembly instructions that perform the function. Under this abstraction, the addition of two variables usually involves more than one instruction. Apart from the actual arithmetic operation that accesses internal registers, memory load and store instructions will be needed. Performance improvements result in optimizing those memory accesses using caches. Each memory level trades access latency for storage capacity, so less and less data is available at memories of lower latencies. The job of the programmer and compiler is to ensure that for critical areas of an algorithm the spatial locality of data is high and can be accessed with the lowest latency possible.

It requires considerable effort and performance analysis tools to optimize code for execution time.

The FPGA is massively parallel by nature. Every LUT can execute a different function at the same time, so it is possible to have multiple arithmetic logic units (ALU) executing addition operations, for example is parallel. On a processor, the ALU is shared and these would have to be executed sequentially. Memories can be instantiated close to where they are needed, resulting in high instantaneous memory bandwidth.

The role of high level synthesis tools is to extract the best possible circuit implementation from a C/C++ code that is functionally correct and meets the requirements. It analyzes data dependencies determining which operations could and should execute in each clock cycle. Depending on the targeted clock frequency and FPGA, some operations might take more cycles to complete. This step is called **scheduling**. Next, the hardware resources are determined that implement the scheduled operation best. This is called **binding**. The last step in the synthesis is the **control logic extraction** which creates a finite state machine that controls when the different operations should execute in the design.

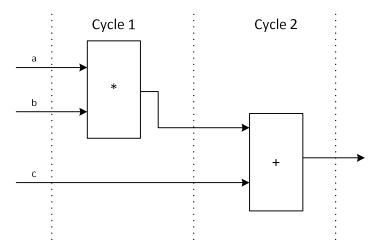

For multi-cycle operations **pipelining** is performed in the scheduling phase. Imagine the following C statement:

x=a\*b+c;

If the clock period is too small for the multiplication and addition to complete in one clock cycle, it will be scheduled for two cycles. For every set of inputs a, b, and c it takes two cycles to obtain the result. It follows that in cycle 2 the multiplier does not perform any operation; it only provides the result calculated in the previous cycle.

This inefficiency becomes more apparent, when this statement is executed in a loop, ie. the circuit processes more than one set of input data.

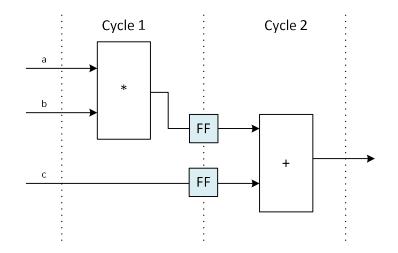

If there was a storage element between cycles, the result from cycle 1 would be saved, and the multiplier would be free to perform a calculation for the next set of inputs. This concept is called pipelining and it is a major optimization opportunity increasing the throughput tremendously.

#### 2.3 Performance metrics

The previous example is a great opportunity to introduce some performance metrics definitions. The **latency** of the statement above is two, as it takes two cycles to output the result. In the first non-pipelined case the **initiation interval (II)** is also two, since it takes two cycles for the circuit to accept a new set of inputs. However, in the second pipelined case the II is just one, because the circuit is able to accept a new set of inputs in every cycle, and will output a result in every cycle. The latency is still two, as the result for the first set of inputs will appear after two cycles. If the circuit processes 10 sets of input data, the non-pipelined versions will have a total latency of 20 cycles ((#-1) \* II + latency). The pipelined versions will only take 11 cycles ((#-1) \* II + latency) to provide all the 10 results.

These performance metrics are calculated by the tools for both loops and functions, and are considered the most important feedback mechanism for the designer to evaluate the synthesized hardware circuit.

## **3 Vivado HLS**

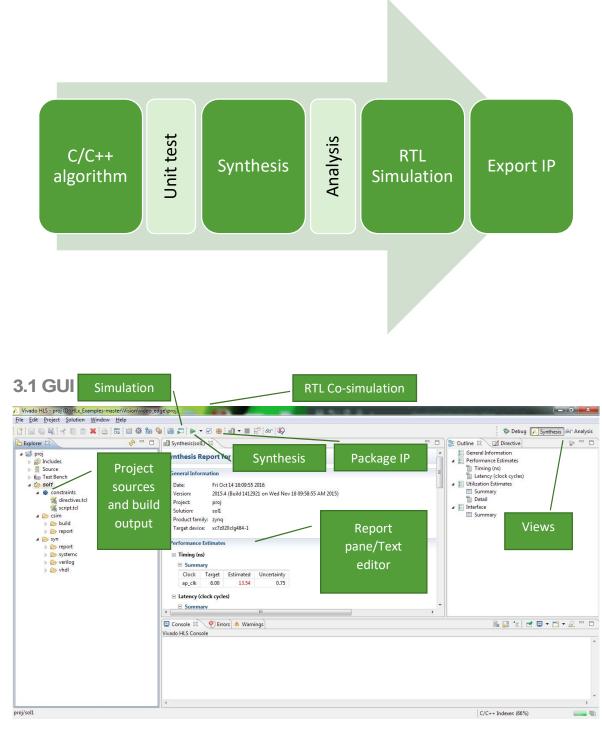

Xilinx's offering in high-level synthesis is part of the Vivado suite and is called Vivado HLS. The workflow is an iterative approach with simulations as verification steps inserted along the way to make sure the design meets the requirements and is functionally correct right from the initial stages. Vivado HLS can:

- compile, execute and debug the C/C++ algorithm,

- synthesize into RTL implementation,

- provide analysis features,

- generate and execute RTL simulation testbenches,

• export the RTL implementation as an IP module.

The GUI layout is quite similar to other software IDEs. The project explorer lists the source, include and testbench files. Simulation and synthesis outputs are also visible here grouped into solutions. The workflow action buttons are in the toolbar ordered by their sequence in the workflow. In the upper right corner three layout views are available each fitting the current workflow step.

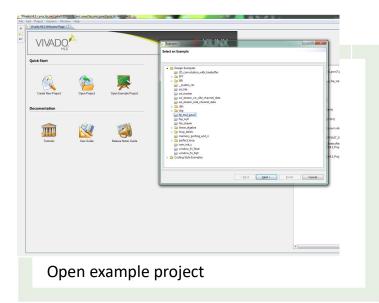

## 4 Task One – Getting familiar with the interface

Let us open an example project to get more familiar with the interface.

Launch Vivado HLS 2015.4 from the Start Menu.

On Linux run vivado\_hls from the shell.

Click the Open Example Project button on the Welcome Page.

Choose Design Examples/fp\_mul\_pow2 from the list of projects

| 🔥 Examples                                                                       |                    |        |                                                                         |

|----------------------------------------------------------------------------------|--------------------|--------|-------------------------------------------------------------------------|

| Specify Example Project Location<br>Specify where to create the example project. |                    | AG     |                                                                         |

| Project name: [fp_mul_pow2                                                       |                    | Browse | Browse to the location of<br>your choice on your local<br>storage drive |

|                                                                                  |                    |        | You may choose<br>zybo_workshop/hls_projec<br>for location.<br>Click OK |

|                                                                                  | Back Next > Finish | Cancel |                                                                         |

| Save project                                                                     |                    |        |                                                                         |

|                                                                                  |                    |        |                                                                         |

| Explorer      Complete Reproduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 128 double_num_t x_num, prod;<br>129<br>130 x num.fp num = x;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Image: Section of the sectio | Open fp_mul_pow2.h<br>below Includes.                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| C/Xiime/Vivado,HLS/2015.4/mog/     C/Xiime/Vivado,HLS/2015.4/mog/     C/Xiime/Vivado,HLS/2015.4/mog/     C/Xiime/Vivado,HLS/2015.4/mog/     C/Xiime/Vivado,HLS/2015.4/mog/     C/Xiime/Vivado,HLS/2015.4/mig/     D/mig/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_powl/p_mul_pow | <pre>111 stringer 45% Pr_MTULE_DOUDCE_TSTS<br/>16 (r_unabsorp = 0.077   (r_unabsorp = 0.077   (r_unabsorp = 0.077   (r_unabsorp = 0.077   (r_unabsorp = 0.077 - 0.077   (r_unabsorp = 0.077   (r_unabsor</pre> | e over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Open fp_mul_pow2.c<br>below Source.                            |

| Girkinfg.mul.pon2.frg.mul.po     Girkinfg.mul.pon2.frg.mul.po     Girkinfg.mul.pon2.frg     | 10     } cbse       10     prod.sign = x_punction;       10     prod.sign = x_punction;       10     prod.sign = x_punction;       10     prod.sign = x_punction;       101     prod.sign = x_punction;       102     prod.sign = x_punction;       103     cetum prod.fp.run;       104     cetum prod.fp.run;       105     cetum prod.fp.run;       106     cetum prod.fp.run;       107     @ Creact R:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Open<br>fp_mul_pow2_test.c<br>below Test Bench.                |

| > 🍙 report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Vivade HS Centole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | *<br>*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Notice that we are in the Synthesis view (upper right corner). |

A Vivado HLS project is much like any other C/C++ software project. There is a source file defining two functions, a header file declaring the functions and some data types. There is also a test bench source file, which is a regular application with a main entry point that runs test on the functions, validating them on functional correctness. Test benches are used for C simulation, which is the first validation step in the design process. The successfulness of C simulation is determined by the return value of the test bench. It is expected to return 0 for a success, and any non-zero value for failure.

Discuss the implementation of the double\_mul\_pow2 function and the test bench.

| C Simulation Dialog  | 4                                    |

|----------------------|--------------------------------------|

|                      |                                      |

| f<br>Options         | E E                                  |

| 🕅 Launch Debugger    | pi                                   |

| e 🔄 Build Only       |                                      |

| 🔄 🕅 Clean Build      |                                      |

| i 🔲 Optimizing Compi | le                                   |

| input Arguments      |                                      |

|                      | 🔲 Do not show this dialog box again. |

| e                    | OK Cancel                            |

| 1                    | UK Cancer                            |

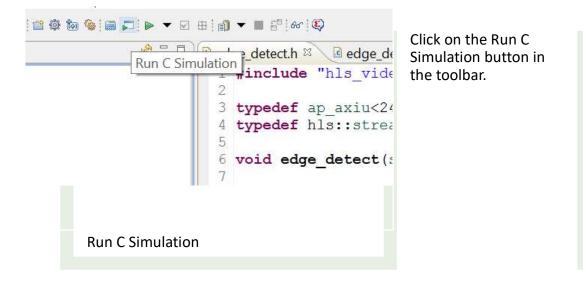

Click the Run C Simulation button on the toolbar.

Leave simulation options at their default values and click OK

Discuss the results of the C simulation and the messages shown in the console.

| 📮 Console 🖾 🔍 👰 Errors 💧 Warnings                                |     |       |     |    |      |     |         | <b>=36</b> (6).E | 1   | z   🛃 🗳 🕶 🙆         | 2 H |

|------------------------------------------------------------------|-----|-------|-----|----|------|-----|---------|------------------|-----|---------------------|-----|

| /ivado HLS Console                                               |     |       |     |    |      |     |         |                  |     |                     |     |

| Compiling(apcc)///fp mul pow2.c in debug                         |     | aba   |     |    |      |     |         |                  |     |                     |     |

| <pre>@I [HLS-10] Running 'c:/Xilinx/Vivado HLS/2015.4/bin/</pre> |     |       | ed. | wi | 64 ( | n/a | ncc ev  | . '              |     |                     |     |

| for user 'Elod' on host 'elap' (Windows N                        |     |       |     |    |      |     |         |                  | v 1 | 0 14.03.19 +0200 20 | 16  |

| in directory 'D:/hls/fp mul pow2/fp mul p                        |     |       |     |    |      |     |         |                  |     |                     | 10  |

| @I [APCC-3] Tmp directory is apcc db                             | 0   | - pro | J'  | P- |      |     | 2, 2014 | c romr           |     | in, build           |     |

| @I [APCC-1] APCC is done.                                        |     |       |     |    |      |     |         |                  |     |                     |     |

| Generating csim.exe                                              |     |       |     |    |      |     |         |                  |     |                     |     |

| hw result = 4.57764e-005 : bits = 0x3F08000000000000             | :   | sign  | =   | +. | exp  | =   | -15,    | mant             | =   | 0x08000000000000    |     |

| hw_result = 5.06868e+250 : bits = 0x73FC515880000000             | :   | sign  | =   | +, | exp  | =   | 832,    | mant             | =   | 0x0C515880000000    |     |

| hw result = -7.0227e-111 : bits = 0xA910E39140000000             | :   | sign  | =   | -, | exp  | =   | -366,   | mant             | =   | 0x00E39140000000    |     |

| hw_result = 2.682e+205 : bits = 0x6A9562BA20000000               |     | sign  | =   | +, | exp  | =   | 682,    | mant             | =   | 0x0562BA20000000    |     |

| hw result = -1.7309e-150 : bits = 0xA0D6A9E380000000             | :   | sign  | =   | -, | exp  | =   | -498,   | mant             | =   | 0x06A9E380000000    |     |

| hw_result = -1.10749e-225 : bits = 0x913A3C65E0000000            | :   | sign  | =   | -, | exp  | =   | -748,   | mant             | =   | 0x0A3C65E0000000    |     |

| hw_result = 2.11551e-204 : bits = 0x15A5398680000000             | :   | sign  | =   | +, | exp  | =   | -677,   | mant             | =   | 0x05398680000000    |     |

| hw_result = 1.82008e-195 : bits = 0x178101B200000000             | :   | sign  | =   | +, | exp  | =   | -647,   | mant             | =   | 0x0101B200000000    |     |

| hw_result = 3.58909e+261 : bits = 0x763D2DCB40000000             | :   | sign  | =   | +, | exp  | =   | 868,    | mant             | =   | 0x0D2DCB40000000    |     |

| hw_result = 7.93181e-005 : bits = 0x3F14CAF280000000             | :   | sign  | =   | +, | exp  | =   | -14,    | mant             | =   | 0x04CAF280000000    |     |

| hw_result = -4.16729e-134 : bits = 0xA43E4A1B80000000            |     |       |     |    |      |     |         |                  |     |                     |     |

| hw_result = 5.09937e+176 : bits = 0x64A01B8680000000             | :   | sign  | =   | +, | exp  | =   | 587,    | mant             | =   | 0x001B8680000000    |     |

| hw_result = 6.96589e-138 : bits = 0x2374BD0560000000             |     | 0     |     |    | 10.0 |     |         |                  |     |                     |     |

| hw_result = -3.3959e+111 : bits = 0xD71697D580000000             |     |       |     |    |      |     |         |                  |     |                     |     |

| hw_result = 1.22026e-079 : bits = 0x2F8CEFFDA0000000             |     |       |     |    |      |     |         |                  |     |                     |     |

| hw_result = -4.15363e-081 : bits = 0xAF3F851E60000000            | :   | sign  | =   | -, | exp  | =   | -268,   | mant             | =   | 0x0F851E60000000    |     |

| *** Test passed ***                                              |     |       |     |    |      |     |         |                  |     |                     |     |

| @I [SIM-1] CSim done with 0 errors.                              |     |       |     |    |      |     |         |                  |     |                     | -   |

|                                                                  | 111 |       |     |    |      |     |         |                  |     |                     |     |

| C Simulation       | 5                                    | Click the Run C<br>Simulation button of the toolbar. |

|--------------------|--------------------------------------|------------------------------------------------------|

| Options            |                                      | the toolbal.                                         |

| Launch Debugger    |                                      | Check the Launch                                     |

| Build Only         |                                      | Debugger option a                                    |

| 🔄 Clean Build      |                                      |                                                      |

| Optimizing Compile |                                      | click OK                                             |

| Input Arguments    |                                      |                                                      |

|                    | 🔲 Do not show this dialog box again. |                                                      |

|                    | OK Cancel                            |                                                      |

| 5 K                |                                      |                                                      |

Notice how the Debug view gets activated, the test bench started and stop at the first instruction of the main function. The test bench can be run step-by-step, breakpoints set, variables and expressions evaluated just like any other software project.

Double click on the blue column in line 109 to place a breakpoint at the line that calls the double\_mul\_pow2 function.

Click the Resume button in the toolbar to run the test bench until the breakpoint is hit

Step into the double\_mul\_pow2 function

Notice how the variables test\_val and test\_exp changed before the breakpoint was hit.

Click the Step Into button in the toolbar or press F5 on your keyboard.

Keep pressing F6 to execute the function statement-by-statement.

Notice how solution1 in the project view has a csim folder now. Synthesis directives and simulation/synthesis results are grouped into solutions. Having multiple solutions allows us to try different settings, devices, clock periods on the same set of source files and analyze the results for each.

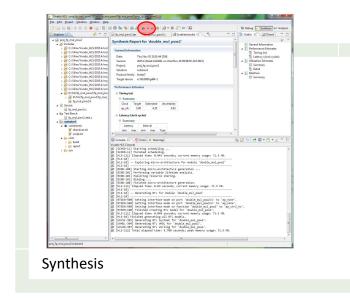

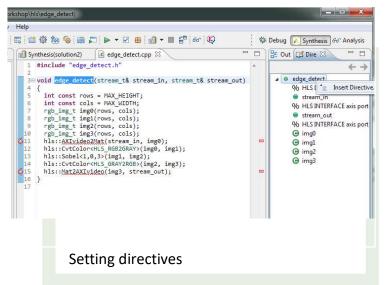

Synthesize the design by clicking the C Synthesis button in the toolbar.

Watch the messages in the console until synthesis completes.

Notice the new syn folder in solution1 and the Synthesis Report that opened automatically.

Discuss the report. What did HLS synthesize? What are the latency and interval values? What are the interfaces that got generated?

| 🗄 Module Hierarchy 🛛 🖻 🔍 🗆                                                        | 🗊 Synthesis(solut 🕞 Performance(sol 🗵 🐂 😐 🗆                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| BRAM         DSP         FF         LUT         Latency         Intervi <ul></ul> | Current Module : double_mul_pow2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Open the Analysis view. |

| e m Petersana Potte 27 E Resource Potte 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0       | Department (construct term)         CO         C1           1         n_cread (read)            2         n_cread (read)            3         trp_(c)            6         org_(c)            7         trp_(c)            8         org_(c)            9         stit(unp)            10         st_t_upp(cons)            11         st_t_upp(cons)            12         org_(t)            13         st_t_upp_(descoptan)()            14         st_t_upg_(descoptan)()            15         reav(*)            18         st_t_upg7(4) |                         |

|                                                                                   | 19 prod 1 in (select) -<br>Performance Resource                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

|                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

|                                                                                   | Properties S E Properties S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         |

|                                                                                   | Property Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |

| 4 <u> </u>                                                                        | · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |

| Analysis                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

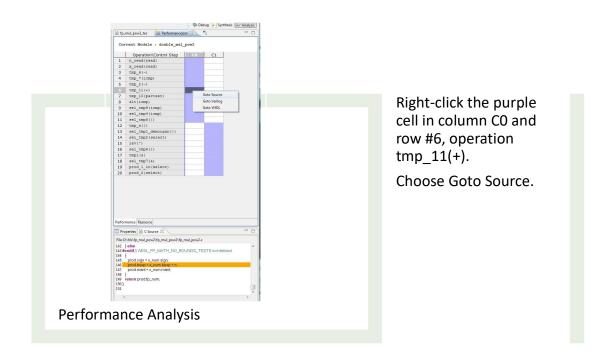

The Analysis view helps in understanding and evaluating the synthesized design. The synthesized modules and loops can be seen on the left, along with timing and logic utilization information. In this case double\_mul\_pow2 does not have any sub-blocks, it is a flat function. Selecting an item will bring up the Performance view on the right. This shows the control states of the logic (C0, C1) and each operation that is scheduled to execute in that state.

When the synthesized design satisfies all the project requirements, the next step is running an RTL simulation to verify that it is functionally correct. In Vivado HLS terminology this is called C/RTL Cosimulation. Vivado HLS is capable of automatically generating an RTL test bench by running the C test bench and using the inputs from there as stimuli and the outputs as expected values.

| Verligs VHOL Simulator Selection | Click on the C/RTL<br>Cosimulation button on<br>the toolbar<br>Choose "all" for the<br>Dump Trace option<br>Click OK.<br>Review the messages in<br>Console |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

The Dump Trace option will export the RTL simulation waveforms that can be opened in Vivado Simulator, for example.

| • ☑ 册 : ப → 🖬 🗗 : 6♂ : 🗐<br>on(solu 🖾 → ³<br>Open Wave Viewer)<br>'double mul pow2' | Click on the Open<br>Wave Viewer button<br>on the toolbar<br>Wait for Vivado to<br>open<br>Open the Window<br>menu and go to<br>Waveform |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| View simulation waveforms                                                           |                                                                                                                                          |

Analyze the simulation waveforms. Look for input values, results. Measure latencies and initiation intervals.

Since the hardware is now validated, all that is left is to package it up into a reusable format.

| A Export RTL Dialog                 |                                    |                                   |

|-------------------------------------|------------------------------------|-----------------------------------|

| Export RTL                          | te<br>ti<br>irr                    | Click on Export RTL               |

| Format Selection<br>n<br>IP Catalog | Configuration                      | button on the toolbar             |

| d Options<br>Evaluate Verilog       |                                    | Leave options on thei<br>defaults |

| d<br>d                              |                                    | Click OK                          |

|                                     |                                    | Wait for export to<br>complete    |

| 1                                   | Do not show this dialog box again. |                                   |

The exported IP files are generated in the active solution folder under impl. Locate the files and explore the sub-folders.

This concludes our first task – Getting familiar with the interface.

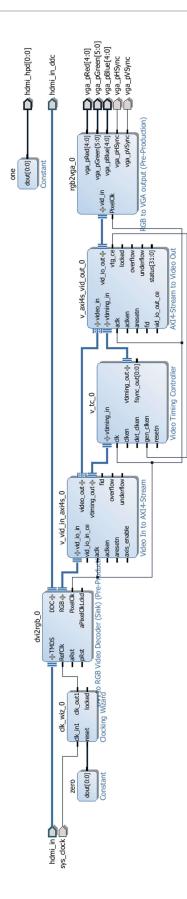

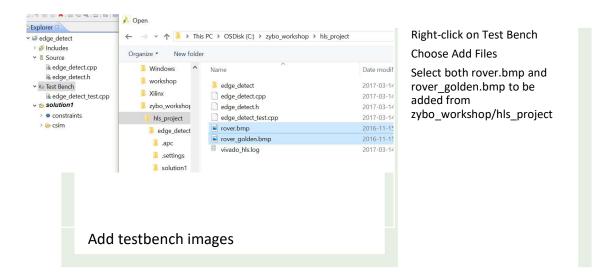

## 5 Task Two – Create a pass-through video pipeline

In this step we are going to create an FPGA project that decodes DVI input and forwards it to the VGA output. This pipeline will serve as the base design that will accept the IP exported from HLS. We are going to create it in Vivado block design re-using IP available from Digilent and Xilinx. The Digilent IPs are available online at <a href="https://github.com/Digilent/vivado-library/archive/master.zip">https://github.com/Digilent/vivado-library/archive/master.zip</a> or among the workshop materials.

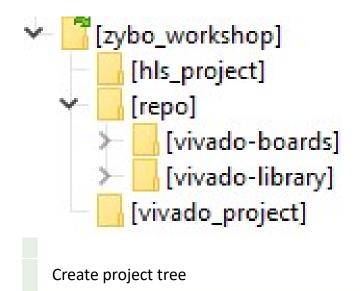

Copy the folder called "zybo\_workshop" to the root of your local hard drive.

If you choose a location other than root, make sure the path has no spaces in it. Take note of the path as you will need it later.

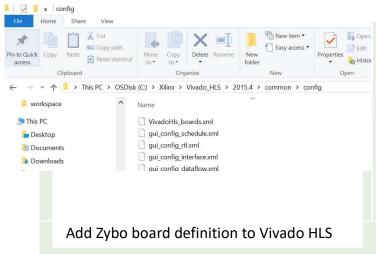

| File Home Share                                                                    | View                                 |                                                                                                                                           |                       |                                      |                                     |                       |                                                         | ~ 0 |

|------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|-------------------------------------|-----------------------|---------------------------------------------------------|-----|

| Pin to Quick Copy Paste access Clipboard                                           | X Cut<br>Copy path<br>Paste shortcut | Move Copy<br>to to Urganize                                                                                                               | New<br>folder         | ₩ New item •<br>Easy access •<br>New | Properties                          | Edit<br>History       | Select all<br>Select none<br>Invert selection<br>Select | n   |

| 🗧 🔶 👻 🛧 🚺 %AP                                                                      | PDATA%\Xilinx\Viv                    | vado∖                                                                                                                                     |                       |                                      | <u>ت</u> ~                          | Search Vivad          | lo                                                      | P   |

| Macromedia<br>Microsoft<br>Mozilla<br>Notepad++<br>Pulse Secure<br>Skype<br>VMware | C:\Users\r                           | hs_err_pid19504.log<br>hw_ila_data_1_3612_1481645525.btr<br>init.tcl<br>ogyorge\AppData\Roaming\Xilinx\Vi<br>earch View Encoding Language | vado\init.<br>Seţting | s <u>M</u> acro <u>R</u> un          | Text D<br>BTREE<br>TCL F<br>Plugins | le<br><u>Window ?</u> | Size<br>36 KB<br>35 KB<br>0 KB<br>1 KB                  |     |

| Xilinx Common                                                                      | init.td 🖾                            | t param board.repoPaths                                                                                                                   | C   ma                |                                      | Contract Contract                   | include a             | -boards/new"                                            | •   |

| ICE                                                                                |                                      | -                                                                                                                                         |                       |                                      |                                     |                       | •                                                       |     |

| ISE<br>PlanAhead<br>updatemem                                                      |                                      |                                                                                                                                           |                       |                                      |                                     |                       |                                                         |     |

| PlanAhead                                                                          | length : 74 lin                      | es:1 Ln:1 Col:7                                                                                                                           |                       |                                      | 1.4180                              | dows (CR LF)          | UTF-8                                                   |     |

Add Digilent board definition files to Vivado

On Windows browse to: %APPDATA%\Xilinx\Vivado\

On Linux cd to: \$HOME/.Xilinx/Vivado/

Copy the provided "init.tcl" there.

If you copied "zybo\_workshop" to a location other than c:\, edit this file. Make sure the path is absolute and use forward slash "/" as path separator even on Windows.

Save the file and close the editor.

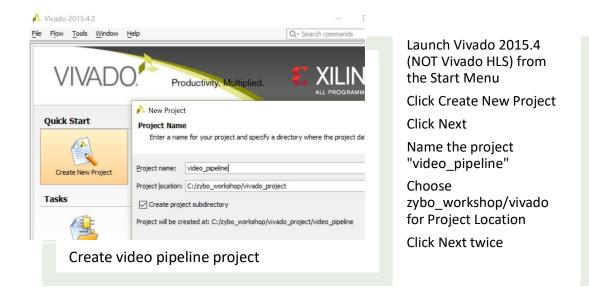

Launch Vivado 2015.4 from the Start Menu

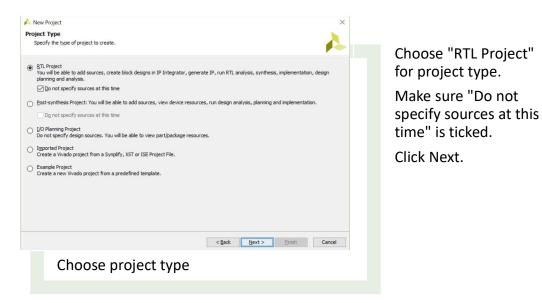

Click Create New Project

Click Next

Name the project "video\_pipeline"

Choose zybo\_workshop/vivado for Project Location

**Click Next**

A New Project Default Part Choose a default Xilinx part or board for your project. This can be changed later Select Boards Select:

Parts Boards

Filter Choose digilentinc.com Vendor: digilentinc.com for Vendor Display Name: All Remaining Board Rey: Latest Reset All Filters Choose Zybo from the Search: Q list below. Bloci RAM Display Name Board Rev Part I/O Pin Count File Ve ndor Basys3 Cmod A7-15t Cmod A7-15t Genesys2 Nexys4 Nexys4 Nexys Video Zedboard xc7a35tcpg236-1

xc7a15tcpg236-1

xc7a15tcpg236-1

xc7a35tcpg236-1

xc7a325tfg900-2

xc7a100tcsg324-1

xc7a100tcsg324-1

xc7a100tcg484-1

xc7a200tbg484-1

xc7a200tbg484-1 ilentinc.com C.0 ilentinc.com B.0 ilentinc.com B.0 236 1.1 50 25 50 445 135 135 365 140 **Click Next** 23 236 nc.com H 900 324 324 484 **Click Finish** com C.1 com A.0 < <<u>Back Next</u> > Einish Cancel Choose the Digilent Zybo as target

If "Zybo" is not showing among the known boards, go back a few steps and make sure init.tcl is installed at the correct location and it has a valid path in it. Restart Vivado and make sure the Tcl Console is showing that init.tcl has been successfully sourced.

🝌 Project Settings

20

Genera

Simulation 80

Elaboratio

8

Synthesis

Bitstrea

IP

+

4

General

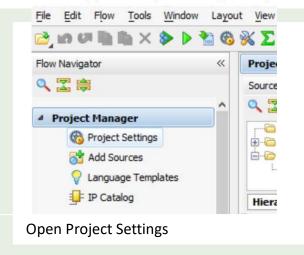

Open Project Settings from the Flow Navigator on the left

🝌 video\_pipeline - [C:/zybo\_workshop/vivado\_pr

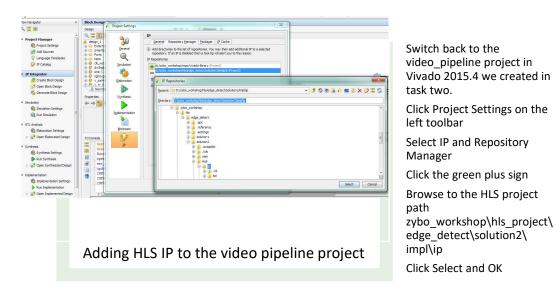

Repository Manager Packager IP Cache Select the IP category (i) Add directories to the list of repositories. You may then add additional IP to a selected repository. If an IP is disabled then a tool-tip will alert you to the reason. Switch to the Repository Manager tab Click the green plus button Browse to the zybo workshop/repo/vivadolibrary folder **Click Select** Vivado will parse the folder and should find IP definitions there Click OK to close Project OK Cancel Apply Settings. Add Digilent IP definitions to Vivado

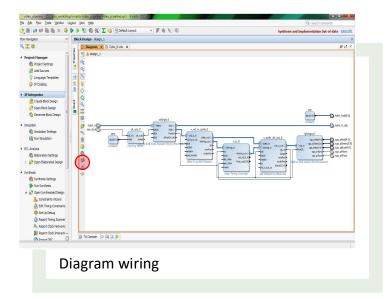

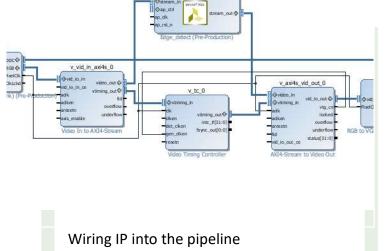

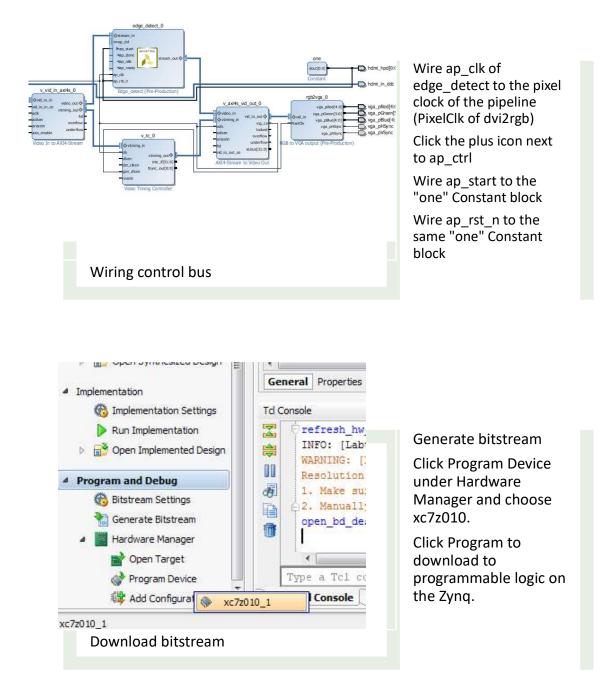

In this project we are going to use the block design flow to create the FPGA design. This helps us reuse any available IP so that we can focus on the processing IP created in HLS. The following IPs are going to be used from Digilent: DVI-to-RGB (DVI Sink), RGB-to-VGA.

And from Xilinx: Video In to AXI4-Stream, AXI4-Stream to Video Out.

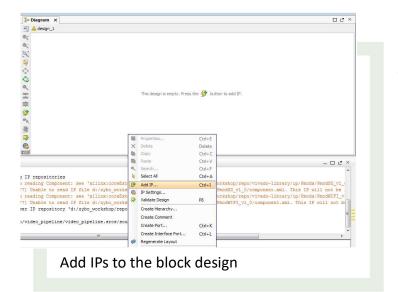

Refresh All

Click Create Block Design on the left toolbar Leave the defaults and

click OK

| No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200     No. 200     No. 200     No. 200       No. 200     No. 200     No. 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Functionary<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Com |

| Survivas sitings     Survivas sitings     Survivas sitings     Survivas sitings     Survivas sites                                                                                                                                                                                                                                                                                                                                                               |

| 1 m /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Teste and ed an P subsystem to the project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Block Design - design\_1 - 🗆 🖻 × 🚰 Diagram 🗙 📳 Zybo\_B.xdc 🔅 Board < ☎ ⊜ ፪ ∞ ♪ ♪ 🔆 🛔 📥 design\_1

Q

Image: Control in the second sec 0+ 0-1 ŵ ₩ P & ī -Block Properties \_ 🗆 🖻 × 9 ← → 🛐 🦎 J dvi2rgb\_0 Name: dvi2rgb\_0 Parent name: design\_1 e General Properties IP ; · · · Use Board interfaces

Click on the Board tab to see the interfaces that are available for the Zybo in board design flow.

Double-click on System Clock

Accept the default of instantiating a new Clocking Wizard

Double-click on HDMI In

Accept the default of instantiating a new DVI to RGB Converter IP

| - Diagram X                                                                                                                |                                                                                                  |                  | 0 e ×                                                                                                                                                  |                                                                    |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| *] 🛕 design_1                                                                                                              |                                                                                                  |                  |                                                                                                                                                        |                                                                    |

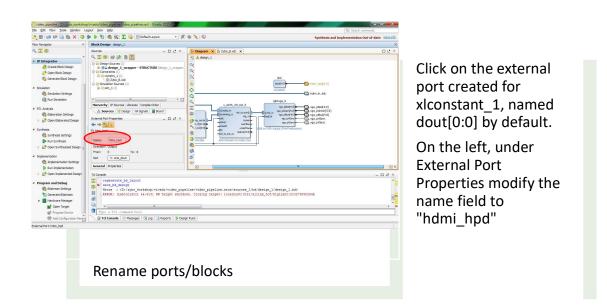

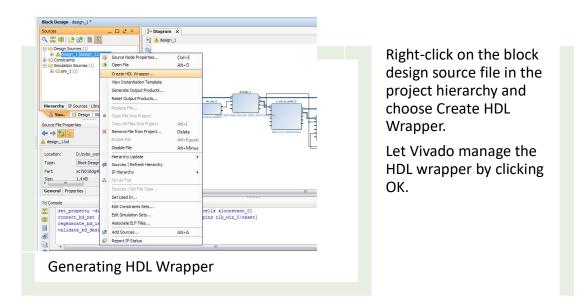

| 2 E S S S S S S S S S S S S S S S S S S                                                                                    | This design is empty. Pres                                                                       | is the 🐓 but     | ton to add IP-                                                                                                                                         | Right-click on an emp<br>space in the diagram<br>and choose Add IP |